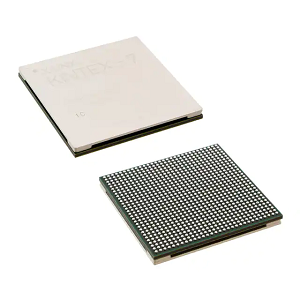

XC7K420T-2FFG901I – Tu'ufa'atasi Circuit, Fa'apipi'i, Field Programmable Faitotoa Fa'atonuga

Uiga Oloa

| ITIGA | FAATAATA |

| vaega | Vaega Fa'atasi (ICs)Fa'amau Fa'atonu Fa'atonu Faitoto'a (FPGAs) |

| gaosimea | AMD |

| fa'asologa | Kintex®-7 |

| afifi | fata |

| Tulaga o oloa | Malosi |

| DigiKey e mafai ona fa'apolokalameina | Le fa'amaonia |

| Numera LAB/CLB | 32575 |

| Numera o elemene/iunite | 416960 |

| Aofa'i le aofa'i o pusi RAM | 30781440 |

| Numera o I/Os | 380 |

| Malosi - Sapalai eletise | 0.97V ~ 1.03V |

| Ituaiga fa'apipi'i | Ituaiga pipii luga |

| O le vevela o galuega | -40°C ~ 100°C (TJ) |

| afifi/Nofo | 900-BBGA, FCBGA |

| Fa'asoa vaega fa'atau | 901-FCBGA (31x31) |

| Numera matai oloa | XC7K420 |

| ITIGA | FAATAATA |

| vaega | Vaega Fa'atasi (ICs)Fa'amau |

| gaosimea | AMD |

| fa'asologa | Kintex®-7 |

| afifi | fata |

| Tulaga o oloa | Malosi |

| DigiKey e mafai ona fa'apolokalameina | Le fa'amaonia |

| Numera LAB/CLB | 32575 |

| Numera o elemene/iunite | 416960 |

| Aofa'i le aofa'i o pusi RAM | 30781440 |

| Numera o I/Os | 380 |

| Malosi - Sapalai eletise | 0.97V ~ 1.03V |

| Ituaiga fa'apipi'i | Ituaiga pipii luga |

| O le vevela o galuega | -40°C ~ 100°C (TJ) |

| afifi/Nofo | 900-BBGA, FCBGA |

| Fa'asoa vaega fa'atau | 901-FCBGA (31x31) |

| Numera matai oloa | XC7K420 |

FPGA

Tulaga lelei

O faʻamanuiaga o FPGA e faʻapea:

(1) FPGAs e aofia ai punaoa faʻapitoa e pei ole logic cell, RAM, multipliers, ma isi. E ala i le faʻatulagaina o nei meafaigaluega faʻapitoa, e mafai ona faʻatinoina le faʻaogaina o masini e pei o le faʻateleina, resitala, faʻasalalauga, ma isi.

(2) FPGAs e mafai ona mamanuina e ala i le faʻaogaina o poloka poloka poʻo le Verilog HDL, mai taʻavale faigofie faitotoa ile FIR poʻo FFT circuits.

(3) FPGAs e mafai ona toe faʻatulagaina e le gata, faʻapipiʻiina se fofo fou i totonu o ni nai selau milliseconds, faʻaaogaina le toe faʻaleleia e faʻaitiitia ai meafaigaluega i luga.

(4) O le faʻaogaina o le FPGA e faʻamoemoeina e le FPGA chip faʻapea foʻi ma le mamanu, ma e mafai ona suia pe suia i se vaʻa vave e faʻafetaui ai ni manaʻoga manaʻomia (e ui, ioe, o le faʻaogaina o taimi e le faʻatapulaʻaina ma e mafai. fa'atuputeleina, ae o lo'o pulea e faiga fa'atekonolosi o lo'o iai nei ma isi mea).

Fa'aletonu

O mea le lelei o FPGA e faʻapea:

(1) FPGA e faʻalagolago i le faʻaogaina o meafaigaluega mo galuega uma ma e le mafai ona faʻatinoina gaioiga e pei o le faʻapipiʻiina o tuʻutuʻuga.

(2) FPGA na'o le fa'atinoina o galuega fa'amautu.

I le aotelega: FPGA faʻalagolago i meafaigaluega e faʻatino ai galuega uma ma e mafai ona faʻatusatusa i tupe meataalo tuʻufaʻatasia i tulaga o le saoasaoa, ae o loʻo i ai se va tele i le mamanu fetuutuunai pe a faʻatusatusa i faʻatonuga lautele.

Gagana faufau ma fa'avae

O masini fa'akomepiuta e mafai ona fa'apolokalameina o masini feavea'i e fa'amaumauina galuega fa'avae ma fa'amatalaga fa'apitoa o talosaga fa'aeletoroni e ala ile tekonolosi EDA.FPGAs, o se tasi o masini faʻapitoa e faʻaogaina ai lenei auala, e faʻaoga saʻo i tagata faʻaoga, matua fetuutuunai ma faʻaoga, faigofie ona faʻaoga, ma vave faʻataʻitaʻi ma faʻatino i meafaigaluega.

Gagana Fa'amatalaga Meafaigaluega (HDL) o se gagana e fa'aaogaina e mamanuina ai masini fa'akomepiuta ma fa'amatala ai ta'aloga fa'afuainumera, o mea autu e masani ona fa'aaogaina o le VHDL, Verilog HDL, System Verilog ma le System C.

I le avea ai o se gagana faʻamatalaga meafaigaluega uma, o le Very High Speed Integrated Circuit Hardware Description Language (VHDL) o loʻo i ai uiga o le tutoʻatasi mai le masini faʻapitoa masini ma tutoatasi mai le fausaga mamanu, faatasi ai ma le lelei o le lautele lautele faʻamatalaga gafatia, e le. faʻalagolago i masini faʻapitoa, ma le mafai ona faʻamatalaina le mamanu o le faʻaogaina o le faʻatonuga faʻapitoa i se tulafono faʻapitoa ma faʻapitoa, ma isi. E lagolagoina e le tele o kamupani EDA ma ua faʻaaogaina lautele i le fanua o le mamanu eletise.fa'aaoga lautele.

VHDL o se gagana maualuga mo le mamanu matagaluega, ma faʻatusatusa i isi gagana faʻamatalaga meafaigaluega, o loʻo i ai uiga o se gagana faigofie, fetuutuunai ma tutoʻatasi mai le mamanu masini, ma avea o se gagana masani faʻamatalaga meafaigaluega mo tekinolosi EDA ma faʻateleina tekinolosi EDA. avanoa i tagata mamanu.

Verilog HDL o se gagana faʻamatalaga faʻamatalaga faʻapitoa e mafai ona faʻaaogaina i le tele o laʻasaga o le faʻatulagaina o meafaigaluega, e aofia ai faʻataʻitaʻiga, faʻasologa ma faʻataʻitaʻiga.

Verilog HDL Avanoa: tutusa ma C, faigofie ona aʻoaʻoina ma fetuutuunai.Ma'ale'ale mata'upu.Tulaga lelei i le tusitusi faʻamalosi ma faʻataʻitaʻiga.Le lelei: tele mea sese e le mafai ona iloa ile taimi faʻapipiʻi.

VHDL Pros: Fa'atonu fa'asologa, manino fa'atonuga.Leaga: umi taimi faamasani, le lava fetuutuunai.

O le polokalama Quartus_II o se si'osi'omaga fa'ata'ita'iga atoatoa e tele-platform na atia'e e Altera, lea e mafai ona fa'amalieina mana'oga o FPGA ma CPLD eseese, ma o se si'osi'omaga atoatoa mo le fa'atulagaina o polokalama fa'apipi'i.

Vivado Design Suite, o se siosiomaga mamanu tuʻufaʻatasia na tuʻuina atu e le tagata faʻatau FPGA Xilinx i le 2012. E aofia ai se siosiomaga faʻapipiʻiina sili ona tuʻufaʻatasia ma se augatupulaga fou o meafaigaluega mai le faiga i le tulaga IC, o loʻo fausia uma i luga o se faʻataʻitaʻiga faʻataʻitaʻiga fefaʻasoaaʻi ma se siosiomaga masani debug.le Xilinx Vivado Design Suite e maua ai le FIFO IP cores e mafai ona faigofie ona faʻaoga i mamanu.